메모리 컨트롤러란?

메모리 컨트롤러는 컴퓨터 시스템에서 중앙 처리 장치(CPU)와 메모리 간의 데이터 통신을 관리하는 장치입니다. 이 컨트롤러는 CPU로부터 메모리 액세스 요청을 받아, 해당 요청을 메모리에 전달하고, 메모리로부터 데이터를 검색하여 CPU로 반환하는 역할을 수행합니다.

메모리 컨트롤러는 메모리 읽기 및 쓰기 작업의 효율성을 극대화하고, 메모리 대역폭과 레이턴시를 최적화하여 전체 시스템 성능에 크게 기여합니다.

메모리 컨트롤러의 기본 이해

1. 주요 기능과 역할

주소 디코딩: 메모리 컨트롤러의 첫 번째 주요 기능은 주소 디코딩입니다. CPU에서 발생하는 메모리 요청은 메모리 주소 형태로 제공되며, 메모리 컨트롤러는 이 주소를 해석하여 실제 메모리의 물리적 위치를 식별합니다.

이 과정은 메모리 매핑, 즉 논리적 주소와 물리적 주소 간의 연결을 설정하는 데 중요합니다.

데이터 읽기/쓰기: 메모리 컨트롤러의 핵심 기능 중 하나는 데이터 읽기 및 쓰기 작업을 처리하는 것입니다. CPU가 메모리로부터 데이터를 읽거나 메모리에 데이터를 쓰기를 요청할 때, 메모리 컨트롤러는 이 요청을 처리하고 요청된 작업을 실행합니다. 이 과정은 데이터 버스를 통해 이루어지며, 데이터의 정확성과 무결성을 보장하는 데 필수적입니다.

캐싱: 또 다른 중요한 기능은 캐싱입니다. 메모리 컨트롤러는 자주 접근하는 데이터를 캐시에 저장함으로써 빠른 데이터 접근을 가능하게 합니다. 캐시는 CPU와 메모리 사이의 속도 차이를 극복하기 위해 설계된 임시 저장소로, 시스템의 성능 향상에 크게 기여합니다.

메모리 보호: 메모리 컨트롤러는 메모리 접근 권한을 체크하여 시스템의 보안을 유지하는 역할도 합니다. 각 메모리 영역에 대해 특정 권한을 설정하고, 이 권한을 기반으로 메모리 접근을 제어합니다. 이는 불법적인 메모리 접근을 방지하고, 시스템의 안정성을 높이는 데 중요합니다.

2. 설계 중요성

메모리 컨트롤러의 설계는 시스템의 전반적인 성능에 결정적인 영향을 미칩니다. 효율적인 메모리 컨트롤러 설계는 시스템의 응답 시간을 단축시키고, 처리량을 높이며, 에너지 효율을 개선할 수 있습니다. 또한, 고급 메모리 컨트롤 기술은 다중 CPU 시스템에서의 메모리 접근 충돌을 최소화하고, 데이터 일관성을 유지하는 데 필수적입니다.

3. 구현 방법

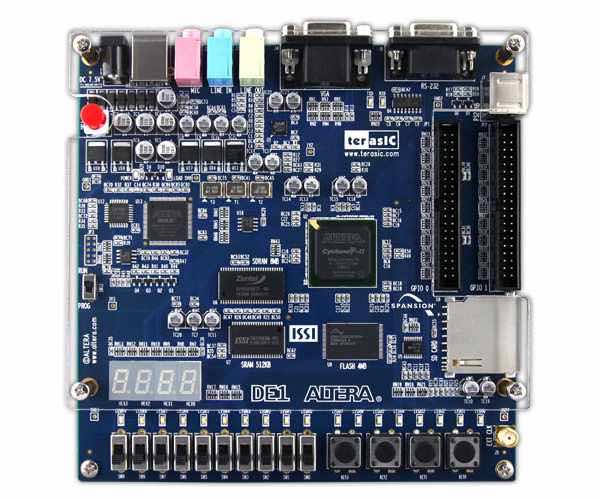

메모리 컨트롤러의 구현은 일반적으로 하드웨어와 소프트웨어 두 가지 측면에서 이루어집니다. 하드웨어 설계는 ASIC(특정 용도의 통합 회로) 또는 FPGA(현장 프로그래밍 가능 게이트 어레이)를 이용하여 수행될 수 있으며, 소프트웨어 설계는 메모리 컨트롤 알고리즘 및 관련 펌웨어 개발을 포함합니다.

예시 코드 1: 기본적인 주소 디코딩

// 주소 디코딩 함수

unsigned int decode_address(unsigned int logical_address) {

unsigned int physical_address = 0;

// 주소 변환 로직 구현

physical_address = logical_address & 0xFFFFF; // 예시 마스킹

return physical_address;

}

예시 코드 2: 데이터 읽기 및 쓰기 처리

// 데이터 읽기 함수

void read_data(unsigned int address, unsigned char *data) {

*data = MEMORY[address]; // 가정된 메모리 배열

}

// 데이터 쓰기 함수

void write_data(unsigned int address, unsigned char data) {

MEMORY[address] = data; // 가정된 메모리 배열

}

예시 코드 3: 캐싱 메커니즘

#define CACHE_SIZE 1024 // 캐시 크기 정의

unsigned char cache[CACHE_SIZE];

// 캐시 초기화

void init_cache() {

memset(cache, 0, sizeof(cache));

}

// 캐시에서 데이터 읽기

unsigned char read_from_cache(unsigned int index) {

if (index < CACHE_SIZE) {

return cache[index];

} else {

return 0; // 캐시 범위 초과 오류 처리

}

}

메모리 컨트롤러의 아키텍처 설계 과정

메모리 컨트롤러 설계는 시스템의 전반적인 성능, 효율성, 그리고 안정성을 결정하는 중요한 과정입니다. 메모리 컨트롤러는 중앙처리장치(CPU)와 메모리 사이의 데이터 흐름을 조절하여, 시스템의 최적 운영을 보장합니다.

이 과정은 복잡하며, 각 단계는 명확하게 정의되고 체계적으로 수행되어야 합니다.

단계 1: 요구 사항 분석

시스템 설계의 첫 번째 단계는 정확한 요구 사항을 파악하는 것입니다. 이 단계에서는 시스템이 지원해야 할 메모리 유형, 메모리 크기, 성능 기준, 그리고 예상되는 사용 환경을 철저히 분석합니다.

메모리 유형의 결정: 메모리 컨트롤러는 다양한 유형의 메모리를 지원할 수 있어야 합니다. 예를 들어, DRAM, SRAM, Flash 메모리 등이 있으며, 각각의 특성과 요구 사항을 이해하는 것이 중요합니다.

성능 목표 설정: 메모리 컨트롤러는 시스템의 전반적인 성능 목표를 달성하기 위해 설계되어야 합니다. 이는 처리량, 응답 시간, 대역폭, 전력 소비 등을 포함할 수 있습니다.

시스템 호환성: 메모리 컨트롤러는 다양한 하드웨어 및 소프트웨어 환경과 호환되어야 합니다. 이를 위해 현재 시스템 아키텍처와의 통합성을 검토하고, 미래의 확장성도 고려해야 합니다.

단계 2: 하드웨어 아키텍처 설계

하드웨어 아키텍처 설계는 메모리 컨트롤러의 물리적 구성을 결정합니다. 이 단계에서는 메모리 인터페이스, 버스 구조, 캐싱 메커니즘 등의 설계가 이루어집니다.

메모리 인터페이스: 메모리 유형에 따라 적합한 메모리 인터페이스를 설계합니다. 예를 들어, DDR 인터페이스는 DRAM에 사용되며, NOR 또는 NAND 인터페이스는 Flash 메모리에 적합합니다.

버스 구조: 메모리 컨트롤러와 CPU, 그리고 다른 주변 장치 사이의 데이터 전송을 위한 버스 구조를 설계합니다. 이는 데이터의 효율적인 흐름을 보장하고, 시스템의 병목 현상을 최소화하는 데 중요합니다.

캐싱 메커니즘: 자주 사용되는 데이터를 효율적으로 관리하기 위한 캐싱 메커니즘을 개발합니다. 이는 시스템의 응답 시간을 개선하고, 전체적인 성능을 향상시키는 데 기여합니다.

단계 3: 소프트웨어 및 펌웨어 설계

소프트웨어 및 펌웨어 설계 단계에서는 메모리 컨트롤러의 운영을 위한 프로그램과 알고리즘을 개발합니다. 이 단계는 메모리 접근 로직과 데이터 관리 알고리즘을 포함하며, 컨트롤러의 효율성과 성능을 최적화합니다.

메모리 관리 알고리즘: 메모리 할당, 회수 및 최적화를 위한 알고리즘을 개발합니다. 이는 메모리의 사용 효율을 최대화하고, 시스템 리소스를 효과적으로 관리하는 데 중요합니다.

펌웨어 구현: 메모리 컨트롤러의 기본적인 운영을 위한 펌웨어를 구현합니다. 이는 하드웨어 레벨에서의 메모리 관리 기능을 지원하며, 시스템의 안정성과 보안을 강화합니다.

성능 최적화: 메모리 컨트롤러의 성능을 분석하고 평가하여, 필요한 경우 최적화를 수행합니다. 이 과정에서는 시뮬레이션 도구를 사용하여 다양한 시나리오에서의 성능을 테스트할 수 있습니다.

VHDL을 활용한 메모리 컨트롤러 설계의 심층 분석

메모리 컨트롤러는 컴퓨터 시스템의 핵심 구성 요소 중 하나로, 데이터의 저장 및 검색 작업을 관리하여 CPU와 메모리 간의 데이터 흐름을 최적화합니다. 이 글에서는 VHDL(Very High-Speed Integrated Circuit Hardware Description Language)을 사용하여 기본적인 메모리 컨트롤러를 설계하는 방법을 자세히 설명하고, 그 과정에서 발생할 수 있는 여러 도전 과제와 해결 전략을 탐구합니다.

1. 메모리 컨트롤러 설계의 중요성

메모리 컨트롤러의 설계는 시스템의 전체적인 성능과 효율성에 직접적인 영향을 미칩니다. CPU가 빠른 속도로 데이터를 처리할 수 있도록 하기 위해, 메모리 컨트롤러는 데이터의 효율적인 이동을 보장해야 하며, 이는 복잡한 로직과 고도의 최적화를 필요로 합니다.

2. VHDL을 사용한 메모리 컨트롤러의 설계 개요

VHDL은 하드웨어 기술 언어로서, 메모리 컨트롤러와 같은 복잡한 디지털 회로를 설계하고 시뮬레이션하는 데 이상적인 도구입니다. VHDL을 사용하여 메모리 컨트롤러를 설계하는 과정은 크게 몇 가지 주요 단계로 나눌 수 있습니다.

단계 1: 요구 사항 정의

시스템의 요구 사항을 명확히 정의하는 것은 설계 과정에서 매우 중요합니다. 이 단계에서는 지원해야 할 메모리 유형, 인터페이스, 필요한 성능 지표 등을 정의합니다.

단계 2: 하드웨어 아키텍처 설계

하드웨어 구성 요소를 설계하는 단계에서는 메모리 인터페이스, 데이터 경로, 버스 구조 및 캐싱 메커니즘을 포함한 아키텍처를 개발합니다. 이러한 요소들은 시스템의 성능과 효율성에 직접적으로 영향을 미치므로, 철저한 계획과 최적화가 필요합니다.

단계 3: 소프트웨어 및 펌웨어 설계

메모리 컨트롤러의 로직과 알고리즘을 개발하는 단계입니다. 이 과정에서는 메모리 접근, 데이터 관리, 오류 감지 및 수정 등의 기능을 구현합니다.

3. VHDL 코드 예시 분석

제공된 VHDL 코드는 메모리 읽기 및 쓰기 작업을 처리하는 기본적인 메모리 컨트롤러의 구조를 보여줍니다. 코드는 다음과 같은 주요 부분으로 구성됩니다:

엔티티 선언 (Entity Declaration)

메모리 컨트롤러의 인터페이스를 정의합니다. 여기에는 클록(clk), 리셋(reset), 메모리 주소(mem_address), 데이터 입력(mem_data_in), 읽기 및 쓰기 신호(mem_read, mem_write), 데이터 출력(mem_data_out), 그리고 작업 완료 신호(mem_ready)가 포함됩니다.

entity Memory_Controller is

Port ( clk : in STD_LOGIC;

reset : in STD_LOGIC;

mem_address : in STD_LOGIC_VECTOR(15 downto 0);

mem_data_in : in STD_LOGIC_VECTOR(7 downto 0);

mem_read : in STD_LOGIC;

mem_write : in STD_LOGIC;

mem_data_out : out STD_LOGIC_VECTOR(7 downto 0);

mem_ready : out STD_LOGIC);

end Memory_Controller;

아키텍처 구현 (Architecture Implementation)

메모리 컨트롤러의 동작을 구현하는 부분으로, 클록 신호의 상승 에지에서 메모리 읽기 및 쓰기 작업을 수행합니다. 리셋 신호가 활성화될 경우, 시스템을 초기 상태로 설정합니다. 메모리 읽기나 쓰기 작업이 요청될 때, 해당 메모리 주소에서 데이터를 읽거나 쓰고, 작업 완료 신호를 mem_ready를 통해 출력합니다.

architecture Behavioral of Memory_Controller is

type RAM_TYPE is array (0 to 65535) of STD_LOGIC_VECTOR(7 downto 0);

signal RAM : RAM_TYPE;

signal data_out : STD_LOGIC_VECTOR(7 downto 0);

begin

process(clk, reset)

begin

if reset = '1' then

-- 초기화 로직

mem_ready <= '0';

data_out <= (others => '0');

elsif rising_edge(clk) then

if mem_read = '1' then

-- 메모리 읽기 연산

data_out <= RAM(to_integer(unsigned(mem_address)));

mem_ready <= '1';

elsif mem_write = '1' then

-- 메모리 쓰기 연산

RAM(to_integer(unsigned(mem_address))) <= mem_data_in;

mem_ready <= '1';

else

mem_ready <= '0';

end if;

end if;

end process;

mem_data_out <= data_out; -- 출력 데이터 지정

end Behavioral;

4. 설계 과정의 도전 과제 및 해결 전략

메모리 컨트롤러 설계 과정에서는 여러 도전 과제가 발생할 수 있습니다. 이러한 도전을 극복하기 위해 다음과 같은 전략을 적용할 수 있습니다:

- 성능 최적화: 시스템의 성능을 극대화하기 위해, 데이터 경로 최적화, 캐시 알고리즘 개선 및 메모리 관리 전략을 지속적으로 개선합니다.

- 테스트 및 검증: 시뮬레이션 및 FPGA 프로토타이핑을 통해 설계를 철저히 테스트하고, 버그를 수정하며 성능을 검증합니다.

- 호환성 유지: 다양한 메모리 유형 및 시스템 환경과의 호환성을 보장하기 위해 유연한 설계 접근 방식을 채택합니다.

성능 최적화 및 테스트: 메모리 컨트롤러 설계의 결정적 단계

메모리 컨트롤러의 성능 최적화 및 테스트는 설계 프로세스에서 매우 중요한 단계입니다. 이 과정을 통해 설계된 컨트롤러의 성능을 실제와 가장 근접하게 평가하고, 예상치 못한 문제를 발견하여 수정할 수 있습니다. 이 섹션에서는 메모리 컨트롤러의 성능 최적화 및 테스트 과정을 상세히 설명하며, 다양한 시뮬레이션 및 벤치마크 테스트 방법을 소개하고, 이를 통해 얻을 수 있는 인사이트와 설계 개선 방안을 탐구합니다.

1. 성능 최적화의 필요성

메모리 컨트롤러의 성능 최적화는 시스템의 전체적인 효율성과 반응성을 향상시키는 데 결정적인 역할을 합니다. 최적화 과정에서는 메모리 접근 시간, 데이터 처리 속도, 대역폭 활용도 등 여러 성능 지표를 개선하는 것이 목표입니다. 이러한 개선을 통해 최종 제품은 더 빠르고, 더 안정적이며, 에너지 효율적인 운영이 가능해집니다.

2. 성능 테스트 및 벤치마킹

성능 테스트는 설계된 메모리 컨트롤러가 사양을 만족하는지 확인하기 위해 필수적인 절차입니다. 이 단계에서는 다음과 같은 테스트 방법을 적용할 수 있습니다.

시뮬레이션 테스트

- 기능 시뮬레이션: VHDL이나 Verilog와 같은 하드웨어 기술 언어로 작성된 모델을 사용하여 메모리 컨트롤러의 기능을 검증합니다. 이 시뮬레이션은 모든 입력과 출력이 예상대로 동작하는지 확인하는 데 사용됩니다.

- 타이밍 시뮬레이션: 메모리 컨트롤러의 타이밍 특성을 분석합니다. 이는 데이터 버스와 메모리 간의 시간 조정 문제를 해결하는 데 중요합니다.

하드웨어 프로토타이핑

- FPGA 프로토타이핑: FPGA를 사용하여 설계된 메모리 컨트롤러를 실제 하드웨어에서 구현하고 테스트합니다. 이 방법을 통해 실제 운영 환경에서의 성능과 호환성 문제를 발견할 수 있습니다.

벤치마크 테스트

- 표준 벤치마크: 다양한 벤치마크 도구를 사용하여 메모리 컨트롤러의 성능을 측정합니다. 이러한 벤치마크는 대역폭, 처리량, 지연 시간 등을 포함한 여러 성능 지표에 대한 실제 데이터를 제공합니다.

3. 데이터 분석 및 성능 지표

테스트 결과의 데이터를 분석하는 것은 성능 최적화 과정에서 중요한 단계입니다. 이 데이터를 통해 메모리 컨트롤러의 각 부분이 목표 성능을 달성하고 있는지, 어떤 영역에서 문제가 발생하고 있는지를 파악할 수 있습니다. 분석된 데이터는 다음과 같은 성능 지표로 표현될 수 있습니다.

- 읽기/쓰기 처리량: 초당 처리할 수 있는 최대 읽기/쓰기 작업의 수.

- 대역폭 사용률: 사용 가능한 최대 메모리 대역폭 대비 실제 사용량.

- 접근 지연 시간: 메모리 요청을 처리하는 데 걸리는 평균 시간.

4. 성능 개선 및 최적화 전략

테스트와 데이터 분석을 통해 도출된 문제점을 해결하기 위한 성능 개선 전략을 개발합니다. 이러한 전략에는 하드웨어 및 소프트웨어 수정, 알고리즘 최적화, 시스템 구성의 조정 등이 포함될 수 있습니다. 개선 작업은 반복적으로 수행되며, 각 반복 후에 성능이 개선되었는지를 확인하기 위해 추가 테스트가 필요합니다.

결론: 메모리 컨트롤러 설계의 중요성 및 전략적 접근

메모리 컨트롤러 설계는 모든 디지털 시스템의 핵심 구성 요소로서, 시스템의 성능, 효율성, 그리고 안정성에 깊은 영향을 미치는 중요한 과정입니다. 이는 단순히 하드웨어 레벨에서의 기술적 실행을 넘어서 시스템의 전반적인 작동 방식과 직접적으로 관련이 있으며, 최적의 메모리 접근성과 데이터 처리 속도를 보장하는 데 필수적입니다.

시스템 성능에 대한 영향

메모리 컨트롤러의 설계는 CPU와 메모리 간의 효율적인 데이터 흐름을 조정함으로써, 시스템의 반응 시간과 처리 능력을 크게 향상시킵니다. 이는 고성능 컴퓨팅 환경에서는 물론, 모바일 및 임베디드 시스템에서도 매우 중요한 요소입니다. 설계 과정에서의 세심한 최적화 작업은 전력 소비를 줄이고, 시스템의 전체적인 에너지 효율을 개선하는 데도 기여합니다.

설계 과정의 복잡성

메모리 컨트롤러 설계는 복잡한 과정이며, 다양한 요구 사항과 기술적 제약 사항을 충족시켜야 합니다. 이는 다음과 같은 여러 측면을 포함합니다:

- 하드웨어와 소프트웨어의 통합: 메모리 컨트롤러의 설계는 하드웨어 구성 요소와 소프트웨어 로직의 효과적인 통합을 요구합니다. 이는 시스템의 요구 사항에 맞춰 세심하게 조정되어야 하며, VHDL이나 Verilog와 같은 하드웨어 설명 언어를 통해 구현됩니다.

- 성능 및 효율성의 균형: 최적의 성능과 효율성을 달성하기 위해서는 시스템의 목표에 맞게 메모리 접근 방식과 데이터 처리 전략을 조정해야 합니다. 이는 메모리 컨트롤러가 다루어야 할 데이터의 양과 유형에 따라 달라질 수 있습니다.

- 테스트 및 검증: 설계된 메모리 컨트롤러는 철저한 테스트와 검증 과정을 거쳐야 합니다. 이는 시뮬레이션, 프로토타이핑, 그리고 벤치마크를 통해 이루어지며, 실제 하드웨어 환경에서의 성능을 확인하고 필요한 수정을 가하는 데 중요합니다.

초보자를 위한 접근 방법

메모리 컨트롤러 설계에 접근하는 초보자는 기본적인 디지털 설계 지식과 함께, 하드웨어 설명 언어에 대한 이해가 필요합니다. 시작하기 위해 다음과 같은 단계를 고려할 수 있습니다:

- 기본 디지털 로직 및 회로 설계 이해: 논리 게이트, 플립플롭, 카운터 등 기본적인 디지털 회로 구성 요소에 대한 이해를 갖추어야 합니다.

- VHDL 또는 Verilog 학습: 이러한 언어들은 디지털 시스템을 설계하고 시뮬레이션하는 데 사용되며, 메모리 컨트롤러와 같은 복잡한 시스템을 설계하는 데 필수적입니다.

- 작은 프로젝트로 시작: 간단한 메모리 컨트롤러 설계 프로젝트로 시작하여 점차적으로 더 복잡한 시스템으로 이동하며 경험을 쌓는 것이 좋습니다.